在本周举行的 2024年IEEE国际电子会议(IEDM) 上,比利时微电子研究中心(imec)展示了一项突破性的技术创新:基於互补式场效电晶体(CFET)的双列标准单元架构。这种设计采用了两列CFET元件,并共用一层讯号布线墙,成功实现制程简化与显着的面积缩减,为逻辑元件和静态随机存取记忆体(SRAM)开辟了微缩新途径。

|

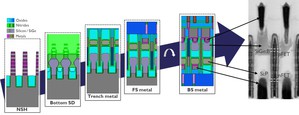

| 这张特写为一颗单片式CFET技术展品的穿透电子显微镜(TEM)影像,该元件制於imec的12寸晶圆研发无尘室(A. Vandooren等人,2024年IEEE国际电子会议) |

根据imec的设计技术协同优化(DTCO)研究,相较於传统单列CFET,双列CFET架构将标准单元高度从4轨缩减至3.5轨。在SRAM单元的应用中,这种设计可实现 15% 的面积缩减,若与14埃米(A14)奈米片技术相比,双列CFET架构的SRAM面积甚至缩减超过 40%。埃米是1奈米10分之1的长度单位。

该技术的核心在於双列CFET元件共用一条中间布线墙(middle routing wall),省去了制造极高深宽比通道的需求,进一步简化了中段制程流程并降低成本。此外,imec的虚拟晶圆厂概念和实验室技术验证,证明此新架构能与现有制程技术顺利接轨。

imec在会议上展示了一颗功能性单片CFET元件,其晶背具备直接连接到底部pMOS元件源极/汲极的接点。这项创新采用了极紫外光(EUV)图形化技术,确保晶背的功率与讯号布线密度,并实现了晶圆正面与晶背接点的高精度对齐(精度小於3奈米)。

imec的DTCO研究计画主持人Geert Hellings表示:「从7埃米逻辑节点开始,CFET元件的应用将取代环绕闸极(GAA)奈米片架构,并为功率、性能和面积(PPA)带来全面提升。透过虚拟与实验制程的结合,我们能确保CFET架构在设计与制造间达到最隹化。」

Hellings进一步指出,双列CFET架构在逻辑和SRAM单元的设计上,每3.7个场效电晶体仅需一个中间布线墙即可满足讯号连接需求,这为未来技术节点的微缩提供了强大支持。

随着半导体业界逐步进入7埃米及以下节点,元件微缩正面临物理极限的挑战,而设计技术协同优化(DTCO)正成为推动技术演进的关键工具。imec此次展示的双列CFET架构,不仅为提升元件密度与性能提供了具体方案,还以其制程创新和可靠性验证,为CFET在逻辑技术中的量产化铺平了道路。