先進的 2.5D / 3D-IC 系統由多塊裸晶、中介層、封裝層和連接基板組成,這使得耦合效應更加具有挑戰性。多晶體異質整合(HI)的出現,將不同的製程技術和電氣特性整合在一起,需要依靠超越現有的設計工具和流程與更強設計和驗證能力。從系統封裝(SIP)到帶有中介層的先進封裝的 2.5D-IC 以及真正的 3D 電路,既有訊號網絡又有電源供應網絡的新興連接架構急需具有超大的數據容量、高度可擴展計算能力與具創新技術的電子設計自動化(EDA) 解決方案。

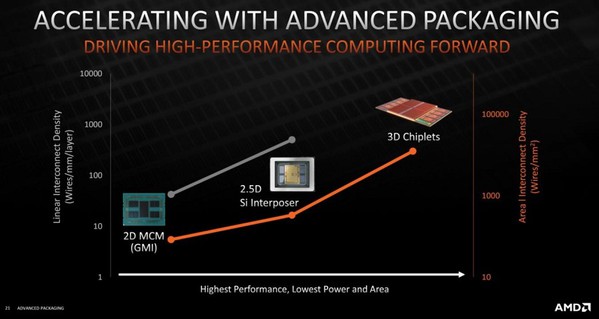

| 圖一 : 2.5D 和 3D-IC 可實現持續擴展、更高性能和更低功耗。 |

|

ACCELERATING WITH ADVANCED PACKAGING

多物理的挑戰

異質多晶架構系統對單晶片上的功耗-性能-面積系統度量標準提出了嶄新、截然不同的挑戰。這可以被看作是電路板設計、封裝設計與晶片設計的綜合挑戰,但是這是一個大家都不熟悉的的新領域—電路板設計師面臨著比傳統電路板具備更高速度、更密集的佈線密度的矽中介層。晶片設計師也面臨著比任何晶片都大一個數量級的幾何尺度,以及新穎的物理問題,如熱管理和電磁訊號完整性。多晶片系統還具有獨特的構造,如穿過矽體的垂直接頭(TSV),它具有電連接和熱導性的用途,所以在設計時更需謹慎考慮。

這樣綜合考量下的結果是一個特別具有挑戰性的多物理設計,需要廣泛的分析工具來涵蓋所有不同的物理學和甚至可能需要重新組織公司資源,將晶片設計團隊、封裝團隊和電路板設計團隊的不同技術集結成一個經整合的設計小組。

本文簡要介紹異質整合設計師將面臨的主要設計問題,並提供新穎的思考方向。

熱完整性

異質整合系統通常將多個高性能晶片擠壓在一個小面積中,其高功耗導致散熱成為可實現性能和整合密度的主要限制因素。用於計算、機器學習(ML)或圖形生成的高性能晶片可耗費數百瓦的功耗,這需要非常嚴格的熱管理。傳統上,熱分析和驗證方法一直是封裝團隊的關注焦點, 但異質整合將熱完整性納入設計實踐的中心,並提出以下挑戰:

‧ 早期在開發原型階段時,會透過熱感知(thermal-aware)的底層佈局,以判定晶片擺放位置、作動預估、自熱和熱傳導。如果兩個發熱晶片放得太近,設計可能因此失敗。

‧ 有效率和準確的全系統熱分析,需要包括散熱元件和外在系統邊界資訊。

‧ 任何小晶片的邊界條件,是由板級的熱分析所判定,其中包括散熱器和計算流體動力學(CFD)來模擬風扇和空氣冷卻。

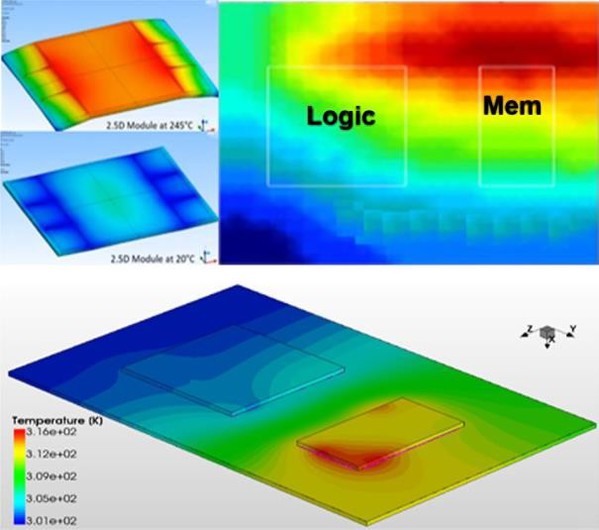

‧ 透過基於實際IC作動概況和最佳化熱傳感器位置的動態熱管理,可以進行功率節流。請記住,考慮到電氣和熱傳播的時間常數存在數量級差異,使用Ansys RedHawk-SC Electrothermal 進行異質整合(HI)系統熱分析的活動曲線時,長時間IC作動模式可以顯示熱梯度和由此產生的機械應力和翹曲。

‧ 作為多元件系統,在多次循環中存在溫度梯度和熱膨脹差異。這是一個主要的可靠度問題,通常需要機械分析工具來模擬封裝基板中的應力和翹曲。

| 圖二 : 使用Ansys RedHawk-SC Electrothermal對異質整合(HI)系統進行熱分析, 長期活動模式顯示熱梯度以及由此產生的機械應力和翹曲。 |

|

電源完整性

異質整合系統的供電網絡(PDN)將多個組件連接在一起,並透過中介層、TSV和數千個微凸塊進行佈線。有鑑於大電流流入小尺寸的異質整合系統中,從而產生高功率密度,因此解決壓降(IR)和電子遷移(EMIR)問題可能極具挑戰性。

‧ 高功率(高達千瓦)以最小的電壓降分配給整個系統。

‧ 異質整合意味著一組異質的電源要求,其包括數位電路、類比電路和IO。

‧ 透過任何單個互連微凸塊或TSV的最大電流是需要被限制的。

‧ 異質整合系統可防止因在系統組裝期間,因帶電人員或組件接觸而導致的靜電放電(ESD)損壞。

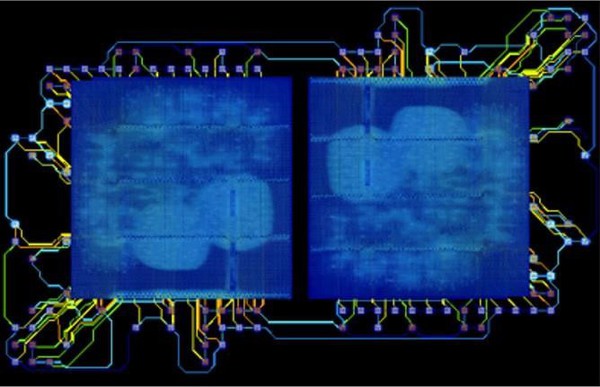

| 圖三 : 透過Ansys RedHawk-SC對雙小晶片進行電源完整性分析2.5D系統顯示電流密度分佈。 |

|

訊號完整性

異質整合系統通常具有各種組件之間的高速互連訊號,包括數位設計、高頻寬IO和射頻(RF)小晶片。在考慮透過矽中介層進行高速佈線時,與單片晶片上的訊號速度相比,兩者之間存在顯著差異—意即,中介層上的佈線長度可以長得多。在這些相對較長的距離上運行高速訊號時,需要進行電磁(EM)分析,以確保其訊號完整性,並捕捉EM 耦合效應。異質整合的訊號完整性包括:

‧ 透過準確的高頻寬訊號網絡分析來實現噪聲感知(noise-aware)小晶片位置擺放。

‧ Chiplet I/O 和chiplet 通訊協定,如UCIe。

‧ 用於類比和數位訊號的小晶片間互連的佈線和屏蔽。

‧ 分析3D小晶片堆疊和中介層/封裝基板上的高速訊號之間的電磁耦合(EMC)、干擾(EMI)和串擾。

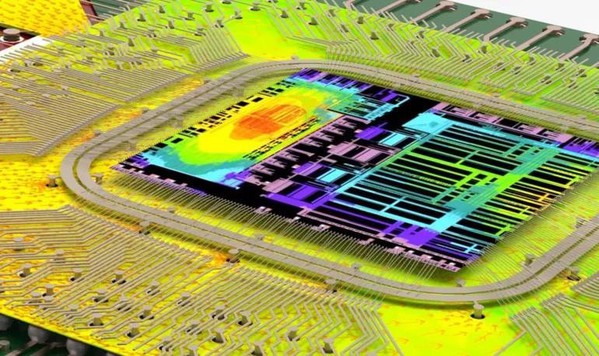

| 圖四 : 使用Ansys SIwav對晶片及其封裝基板進行訊號完整性分析。 |

|

時脈同步和時序收斂

與電源網絡類似,時脈訊號也是整個異質整合系統的全局訊號。時脈分配提出了特殊的設計和驗證挑戰,以確保具有多個頻域和跨大基板區域的小晶片之間的同步。 其中一些時序挑戰包括:

‧ 透過高效的系統級時脈分配最佳化小晶片間的時脈和時脈域。

‧ 維護整個系統範圍的內存記憶體特性一致。

‧ 考慮功率、熱和製程變化條件的系統感知(system-aware)時序收斂。

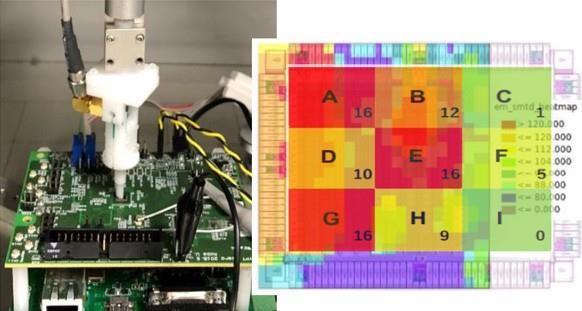

硬體安全

以異質整合系統的分解性質,容易讓惡意攻擊者透過利用側通道漏洞來存取秘密或關鍵任務訊息,這暴露了更多被攻擊的機會。在設計機密數據的儲存或小晶片之間的通訊時,必需有效避免洩漏。與軟體的弱點不同,在於硬體漏洞一旦在晶片製造出來後就無法修復,安全性由設計把關是唯一可行的選擇。多物理場分析可用於評估:

‧ 小晶片之間的潛在隱蔽通道。

‧ 側通道攻擊的漏洞。(側通道是從攜帶訊息的晶片發出的物理效應,可以從外部檢測到,例如,電源噪聲、電磁場、溫度波動等。)

‧ 在異質整合系統中針對大量暴露和易存取的部分(例如中介層)進行物理攻擊。

‧ 針對封裝內的數據洩漏進行監控和檢測。

‧ 預測電源雜訊和其他指標的執行簽章,以驗證製造的正確性和安全性(即檢測插入的木馬或仿冒品)。

| 圖五 : 使用Ansys RedHawk-SC Security模擬的側通道發射與實驗室電磁探頭的結果相符。 |

|

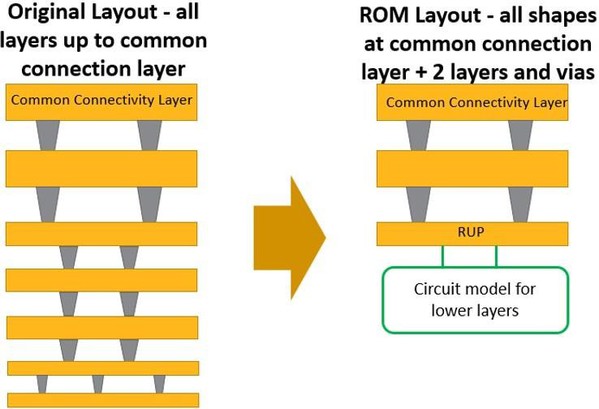

運算容量和降階模型(Reduced Order Models;ROM)

近年來,單晶片變得非常大,但3D異質整合系統依然更大,通常超過工具可負荷的全平面分析能力。有兩種關鍵技術對於處理IC呈指數增長的規模和複雜性至關重要:雲端計算和降階模型。為實現必要的容量,任何異質整合平台都必須進行雲端最佳化,以利用彈性計算的力量作為核心架構功能,而不是事後才考慮。

ROM是異質整合基石的抽象表示,它可以執行完整的系統分析,而不會在準確性方面有任何顯著的損失,並將元件的行為傳達給下一個分析和設計階段。容量和層次結構的一些主要考慮因素,包括:

‧ 低內存佔用,以實現標準雲硬體的最佳使用。

‧ 可以有效利用數百個的可擴展算法計算核心。

‧ 全面的ROM,可捕捉全方位的多物理場效應(功率、電氣、熱、訊號完整性、電磁耦合等)

‧ 在分層概念中考慮不同等級的細節,使複雜的異質整合系統的調適和診斷更加容易和更易於管理。

‧ 透過有選擇性地將某些元素的ROM顯示出來,並完整詳細描述其他元素以最大限度地提高準確性。

| 圖六 : 一個在模塊中佈線的 ROM 範例。 它僅保留連接到端口的頂層路由層,較低層表示為緊湊的電氣模型。 |

|

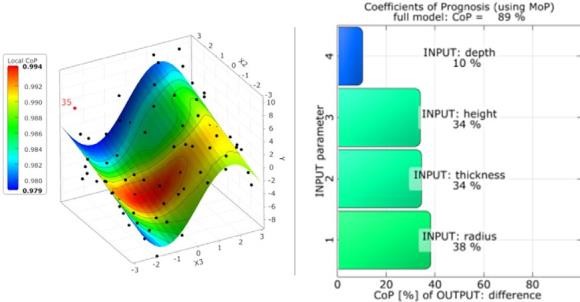

透過機器學習優化系統參數

異質整合系統的完整多物理場分析的規模和複雜性非常驚人,超出了電子設計師的最佳化能力,因為設計選擇的自由度實在是太大了。這就是為什麼3D設計社群已經意識到,由人工智慧(AI)和機器學習(ML)驅動的自動最佳化引擎,對於獲得最佳化的最終結果至關重要。這樣的系統必須有能力處理以下問題:

‧ 同時進行多變量最佳化,包括來自許多不同物理求解器的結果。

‧ AI輔助生成簡化模型以加速設計空間的探索。

‧ 對所有參數進行敏感性分析以確定關鍵的設計選擇。

‧ 靈活的成本函數定義來定義最佳化目標。

| 圖七 : 使用Ansys optiSlang最佳化配電網格幾何參數的靈敏度分析。. |

|

總結

從上面的概述中可以清楚地看出,3D 異質整合是一項複雜的任務,它將各種各樣的晶片級、封裝級和電路板級分析要求匯集到一個巨大的多物理場域中。這非常具有挑戰,沒有一家公司具備一個要素完整的設計流程和一個開放、可擴展的設計平台,而這是在此快速發展的領域中,建立與電子設計相關專業知識的最佳途徑。