Certus-NX 是莱迪思Nexus 技术平台上的第二款产品,它将为更广泛的应用带来FD-SOI 制程的优势。这些通用 FPGA 提供低功耗、小尺寸和灵活的 I/O,PCIe Gen2 和千兆乙太网介面以及高级加密功能。它们适用于智慧家庭、IoT、消费电子网路、马达控制等多个领域的应用。

Certus-NX 将莱迪思 Nexus FPGA 技术平台的优势带到了新市场,主要针对需要 PCI Express 和千兆乙太网互连的应用。新产品系列有两种型号,分别拥有 17K 和 39K 逻辑单元。较大的 Certus-NX-40 还提供 PCIe Gen2 介面,可连接主机处理器、无线或有线通信晶片以及其他许多元件。两种型号均通过硬核支援千兆乙太网,提高了性能和功效。新产品的封装尺寸远小于竞品的同时,I/O 密度增加了一倍。

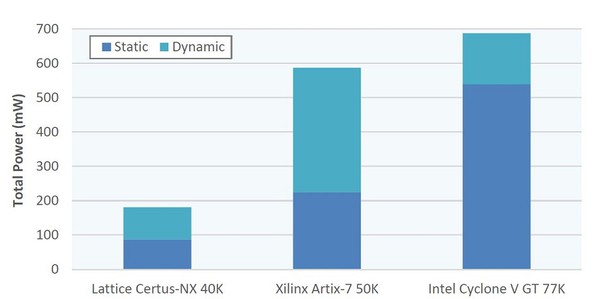

Nexus 平台的独特之处在于采用了 FD-SOI 制程。这与之前的 CMOS 制程相比有很大区别,能够极大降低功耗。如图一所示,Certus-NX 比英特尔和赛灵思的同类产品功耗低3-4倍。 Certus-NX的配置时间极短,能够让系统快速启动。该元件还拥有验证和加密硬体模组提升安全性。

| 图一 : Lattice Certus-NX 器件。与英特尔和赛灵思的类似FPGA产品相比,Certus-NX的功耗降低了 70-75%。此功耗是针对 PCIe Gen2 介面,在严格测试环境下Tj =85oC,125MHz 测得的。(source:供应商功耗计算器) |

|

Certus-NX 主要面向网路中的各类控制和计算应用,包括在网路边缘运行的自动化工业设备以及 5G 通信基础设施和云端资料中心。该 FPGA可以处理多种通信协议,其安全特性非常适合联网设备。在许多情况下,该元件能在执行通信任务时分担神经网路(AI)的负载。 Certus-NX 还可以连接到模拟电机和感测器。

产品概述

Certus-NX FPGA提供了灵活的 I/O 和足够的门电路来实现各种协议。该元件拥有多达39K 逻辑单元,为各类设计提供足够的逻辑从而使用嵌入式 DSP 核实现神经网路或其他加速功能。其硬体加密模组可加速启动代码身份验证的椭圆曲线(ECDSA)加密和 AES 批量加密演算法。该晶片还包括用于时钟和资料恢复(CDR)的硬逻辑,支援高达1 Gbps 的乙太网资料传输速率,更好地支援了乙太网设计。通过结合该模组与足量的 LUT 实现乙太网协定,该晶片还可以实现与外部 PHY 晶片的SGMII 连接。

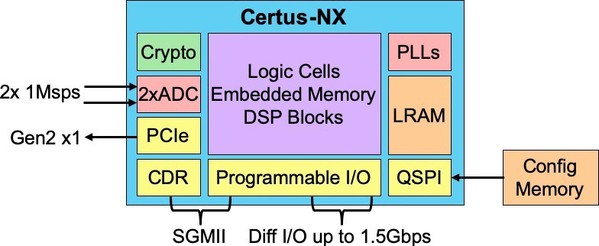

如图二所示,Certus-NX-40 包括了PCIe Gen2 控制器的硬逻辑用于高速通信。该介面可连接单个速率高达 5 Gbps 的通道。两种型号都有两个 12 位逐次逼近(SAR)型模数转换器(ADC),速率高达每秒一百万个采样(Msps)。对于其他协定,该晶片的可程式设计 I/O 可以实现高达 1.5Gbps 的单个介面和差分介面,包括 LVDS、subLVDS 和 DRAM (最高为 DDR3-1066)。对于这些介面,必须使用 LUT 资源实现控制器。晶片的逻辑结构包括LUT、嵌入式记忆体和用于 DSP 功能的 18x18 位乘法器。晶片逻辑机构外拥有一个大型RAM,可提供高达 2.5 Mbit 的额外存储空间。

| 图二 : Certus-NX 示意图。全新 FPGA 拥有实现 AES 和椭圆曲线加密的硬核模组、用於十亿位元乙太网(SGMII)的时钟和资料恢复(CDR)、PCIe Gen2 控制器以及模数转换器(ADC)。 |

|

FD-SOI制程可实现基体偏压(back-bias),与 CMOS制程相比,漏电降低75%。在1.0V电压下工作会降低有效功率。该制程还提高了晶片的可靠性。由于 FPGA 将其配置存储在SRAM 中,因此随机软错误可能会导致元件故障(SEU)。相比于CMOS,FD-SOI制程能够消除SRAM超过 99%的软错误,从根本上避免了 SEU 的发生。

Certus-NX 产品提供各种封装,其中最小尺寸仅为6x6 mm。该设计的低功耗特性减少了电源连接和接地的数量,从而为 I/O 留出更多空间。最小的封装尺寸有 82 个 I/O,最大的封装(14x14 mm)则拥有 192 个 I/O。莱迪思还缩短了将 FPGA 配置载入到 SRAM 所需的时间,从而缩短了启动时间。若使用 Quad-SPI 连接外部快闪记忆体,Certus-NX-40 的启动时间少于 14ms。而 I/O 在 3 毫秒内即可完成初始化。

产品比较

对于需要 PCIe 的应用,Certus-NX-40 与市场上的另两款产品形成竞争关系,即英特尔的Cyclone V 和赛灵思 Artix-7 系列 FPGA。后两者都是具有硬核 PCIe 介面、采用 28nm CMOS 制程的 FPGA。对于这款产品,选择了有 50000 个逻辑单元的型号作为对比, 因为它们下一级较小的型号仅有 33000 个逻辑单元,远低于 Certus-NX。如表一所示,这两款竞品的总存储容量略大,对应的门数也较多,同时还提供更多的 DSP 模组。

?

|

Lattice

Certus-NX-40

|

Intel Cyclone V

5CGXC4

|

Xilinx Artix-7

XC7A50T

|

逻辑单元

|

39000 LC

|

50000 LE

|

52160 LC

|

总 RAM 大小

|

2.5 Mbit

|

2.8 Mbit

|

3.3 Mbit

|

DSP(18x18 乘法器)

|

56

|

140

|

120

|

硬体加密模组

|

AES, ECDSA

|

AES

|

AES

|

PCI Express

|

Gen2 x1

|

Gen1 x2

|

Gen2 x1

|

其他硬核 I/O

|

SGMII, ADC

|

DDR3

|

SGMII, ADC

|

最大 I/O 数量*

|

82–192

|

129–336

|

106–250

|

差分 I/O 速率

|

1500 Mbps

|

840 Mbps

|

1250 Mbps

|

IC 制程

|

28nm FD-SOI

|

28nm CMOS

|

28nm CMOS

|

最小封装尺寸

|

6mm x 6mm

|

11mm x 11mm

|

10mm x 10mm

|

软错误率(FIT)

|

19 次

|

Not reported

|

3102 次

|

配置时间

|

14 ms

|

139 ms

|

173 ms

|

估计功耗

|

181 mW

|

688 mW

|

539 mW

|

表一 用于 PCIe 设计的 FPGA。 Certus-NX 提供更优的加密性能,支援乙太网和更快的 I/O 速度。该范围对应不同封装尺寸;*该资料是针对 PCIe Gen2 介面,在严格测试环境下 Tj =摄氏85度,125MHz 测得的。 (source:除莱迪思外的供应商)

Certus-NX支援最优的加密,提供使用者模式AES 加速以及 FPGA 配置位元流的验证(ECDSA)和加密。英特尔和赛灵思的两款产品缺少验证,仅支援AES配置。尽管Cyclone FPGA的两个PCIe Gen1通道可以提供相同的总频宽,但它不提供PCIe Gen2 支援,并且它不提供用于乙太网设计的硬核 CDR 模组。 Certus-NX 的 I/O 速度最高,其封装尺寸仅为其他产品的三分之一,可大大节省电路板面积。

对于不需要 PCIe 介面的应用,Certus FPGA 则与 Cyclone V E 系列和 Spartan-7 系列两款产品竞争。

表二对比了 Certus-NX-17 与上述系列中逻辑单元数量相似型号。尽管 Certus- NX 的逻辑单元略少,但它的存储空间更大,既有嵌入式记忆体又有外部的大型记忆体, 使其能够缓冲更多资料或存储更大的神经网路。与之前一样,Certus-NX 在加密方面更为突出,I/O 速度更胜一筹。其 6x6 mm 的极小封装尺寸所需的电路板面积不到两款竞品的四分之一,并且 I/O 密度约是它们的两倍。 Certus-NX 也是该组产品中唯一具有乙太网硬核的 FPGA。

?

|

Lattice

Certus-NX-17

|

Intel Cyclone V

5CEA2

|

Xilinx Spartan-7

XC7S25

|

逻辑单元

|

17000 LC

|

25000 LE

|

23360 LC

|

总 RAM 大小

|

3.0 Mbit

|

1. 9Mbit

|

1.9 Mbit

|

DSP(18x18 乘法器)

|

24

|

50

|

80

|

硬体加密模组

|

AES, ECDSA

|

AES

|

AES

|

其他硬核 I/O

|

SGMII, ADC

|

DDR3

|

ADC

|

最大 I/O 引脚数

|

78 I/O

|

223 GPIO

|

150 I/O

|

最大 I/O 密度

|

2.2/mm2

|

1.3/mm2

|

0.9/mm2

|

差分 I/O 速率

|

1500 Mbps

|

840 Mbps

|

1250 Mbps

|

IC 制程

|

28 nm FD-SOI

|

28 nm CMOS

|

28 nm CMOS

|

最小封装尺寸

|

6 mm x 6 mm

|

13 mm x 13 mm

|

13 mm x 13 mm

|

表二 FPGA 用于网路边缘设备。 Certus-NX 拥有更小的封装尺寸,抗软错误性能比竞品高 100 多倍,配置时间缩短 10 多倍。 (source:除莱迪思外的供应商)

Certus-NX 系列产品利用其独特的 FD-SOI 技术优势,在功耗和抗软错误率方面有很大优势。如图 1 所示,在基本的设计实现中,Certus-NX 晶片的功耗比英特尔和赛灵思的产品低 3-4 倍。莱迪思的晶片只出现 19 次软错误故障(FIT),稳定性是其余两款产品的 160 倍。从 quad-SPI 记忆体启动时,Certus-NX 的配置速度也比竞品快 10 倍。其余两款产品均不提供 I/O 引脚瞬时启动功能,而在 Certus-NX 上的回应时间仅为 3 ms。莱迪思还提 供 sensAI 解决方案集合,让客户能够使用 Caffe 或 TensorFlow 工具开发神经网路。我们期待莱迪思今后可以在 Certus-NX 系列元件上提供这些功能。 sensAI 还包括 RTL overlay, 可使用整数或二进位计算对 FPGA 程式设计,进行神经网路推理。

结论

Certus-NX 的诸多优势可直接改善终端产品。其 6x6 mm 的小尺寸封装可用于更小的电路板设计或节省空间便于添加新的系统功能。类似的 FPGA 竞品封装尺寸为 10x10 mm 到13x13 mm,门数相对较少的型号也是如此。尽管 Certus-NX 尺寸很小,但能提供更高的I/O 密度,为电路板设计人员提供了极大的灵活性。该晶片采用独特的 FD-SOI 技术,比CMOS 制程功耗更低,实现了功耗和尺寸和全面优化。

对于通信和其他应用,Certus-NX 提供了硬逻辑实现 PCIe Gen2 和千兆乙太网介面,简化了这些常用标准的实现。该元件灵活的 I/O 引脚速率高达 1.5 Gbps,能比竞品 FPGA 更快地处理通信。

为了提高联网设备的安全性,该系列 FPGA 还拥有加密模组,加速批量加密AES 和椭圆曲线(ECDSA)验证。该模组还可以验证外部配置记忆体,从而实现安全启动。除 Certus-NX 外,没有任何一款逻辑单元少于 100K 个 FPGA 拥有 ECDSA 模组。 Certus-NX 初始化速度也比竞品元件快 10 倍,大大减少了终端使用者等待其设备启动的时间。

全新 FPGA 拥有一个 A/D 转换器,可以搭配 IoT 设计中的模拟感测器。结合 PWM 模式下的可程式设计输出,该ADC很适合用于电机控制。此外,Certus-NX 可以用作加速器,通过莱迪思sensAI 平台或逻辑单元上的特定演算法来实现神经网路。在这些设计中,FPGA可以通过高速PCIe介面直接连接到主机处理器,同时仅占用少量引脚。 FD-SOI 制程对软错误具有天然的免疫力,因此 Certus-NX 是航空航太应用的理想选择。然而,莱迪思的元件乘法器数量较少,不太适合 DSP 密集型应用。

Certus-NX 是基于莱迪思 Nexus 平台的第二款产品,它为广泛的应用领域带来了FD-SOI制程的优势。这些通用FPGA可提供低功耗特性、小尺寸封装和灵活的 I/O 以及 PCIe Gen2、千兆乙太网介面和高级加密功能。它们非常适用于各类网路边缘应用,包括智慧家居、物联网和消费电子网路。此外,它们还可以用于马达控制和其他模拟应用,或者为AI和其他专用演算法提供低功耗高性能的加速服务。

(本文由莱迪思提供,作者Linley Gwennap为林利集团(The Linley Group)首席分析师)