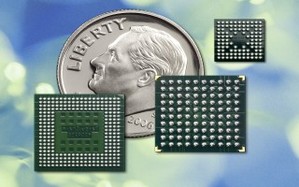

Alter宣佈,公司擴展了MAX II元件系列,以滿足不斷發展的可攜式應用市場的需求;MAX II元件採用了新的超小外形封裝和新型斷電功能,是成本最低的元件,掌上型應用設計人員使用該元件後,成本和功率消耗僅是競爭產品的一半。Altera MAX II CPLD滿足了點對多點(point-to-multipoint, PMP)系統、條碼掃描器、PDA和掌上型感測器等可攜式系統設計人員對小外形封裝和低功率消耗功能的要求。

|

| BigPic:320x200 |

MAX II EPM240、EPM570與EPM1270元件現在提供100接腳和256接腳0.5mm Micro FineLine BGA(MBGA)封裝和100接腳1.0mm FineLine BGA(FBGA)封裝。與競爭CPLD方案相比,設計人員使用新的MBGA封裝後,在相同的電路板面積上,使用者I/O和邏輯單元(LE)數量平均多出50%。這使得MAX II CPLD非常適合單位電路板面積上(mm2)需要較多I/O與LCD顯示器、小鍵盤、快閃記憶體和記憶體等進行介面的應用。設計人員利用新封裝和MAX II元件獨有的特性(較高的邏輯密度、晶片內電壓穩壓器和內部振盪器),能夠進一步降低系統成本,整合獨立元件,減少電源線路的數量。

MAX II CPLD具有最低的動態功率消耗——比競爭CPLD方案的功率消耗低50%以上,還具有能夠延長電池使用時間的斷電功能。與競爭CPLD不同,MAX II元件的功率消耗特性能夠將元件斷電,完全切斷電流接收。

Altera亞太區市場總監梁樂觀表示:「可攜式或者電池供電應用設計人員面臨可編程行業近20年來一直難以解決的挑戰——越來越短的開發週期、行業標準變化導致的功能不確定性,以及成本壓力等。Altera CPLD的零功率消耗模式以及這一市場上通用的封裝形式,能夠幫助可攜式設計人員解決這些問題。」