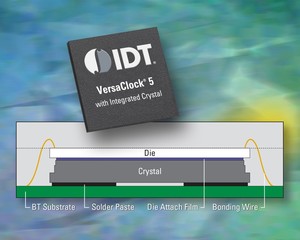

供应关键混合讯号半导体方案模拟与数字公司IDT推出新版VersaClock 5 可程序化频率产生器,其内建晶体设计使电子计时系统更简单更具成本效益。 5P49V5933及 5P49V5935提供了IDT VersaClock 5频率产生器创新的功能,同时藉由晶体整合达到减少电路版的空间及降低成本。 透过整合频率源,设计人员未来在设计时不再需要与外部晶体合并,而将时间花费于因合并继之而来的频率调整上。

|

| IDT推出新版VersaClock 5 可程序化频率产生器,让设计人员可减少电路板空间,物料列表及设计时间 |

VersaClock 5可程序化计时设备只需要一半的核心功耗即可达到最佳抖动效能,并提供独立的标准成对输出,输出型态包括LVDS, LVPECL,HCSL或双LVCMOS。 此多重输出计时解决方案具备相当的设计灵活性整合系统组件,使其适合注重成本,且需低功耗、低抖动应用的设计。 整合晶体有效地将装置转为可程序化石英晶体振荡器,并从设计中将不必要的组件移除。

IDT时序事业群总经理Kris Rausch表示:「我们透过晶体整合至最新版的VersaClock 5装置,开发了具客户优势的独特创新之时序产品。 」「 设计团队取得原始VersaClock 5的所有优势-出色的抖动效能及极低功耗-加上不需处理晶体所省下的时间和成本。 」

5P49V5933最多可提供两个输出频率,而5P49V5935则可提供多达四个。 此装置提供4×4微米封装。 令人印象深刻的700 fsec RMS相位抖动性能满足客户对于1G / 10G以太网络和PCI Express 1,2,3的需求,以及其他高效能芯片互连,并符合SoC和FPGA对于频率产生的需求。 此装置特色为具有仅30毫安的低核心功耗。 (编辑部陈复霞整理)