系統-技術偕同最佳化(system-technology co-optimization,STCO)—透過3D整合技術支援—被視為延續微縮技術發展之路的下一個「開關」。愛美科研究員暨3D系統整合計畫主持人Eric Beyne,以及愛美科3D異質整合計畫主持人Julien Ryckaert,將在本文說明STCO原理、展示3D技術工具箱,並提出兩件具前瞻性的案例:邏輯對記憶體的異質整合(logic on memory)和晶背電源供應(backside power delivery)。

隨DTCO而來的STCO…

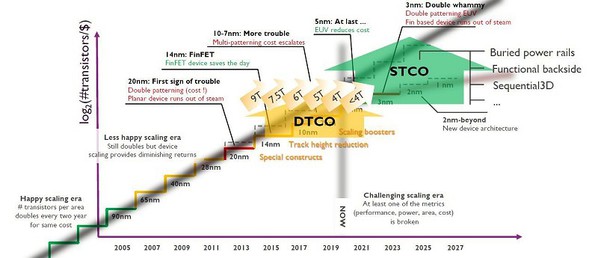

半導體產業活在由摩爾定律驅動的「快樂微縮」時代好幾年了。在這個時代,單就尺寸微縮技術(dimensional scaling),就能帶給每個新技術世代在功耗、性能、面積和成本方面所需的好處。然而,半導體產業在過去15年間,已不再沿著這條微縮技術的康莊大道。尺寸微縮技術的收益開始遞減,劃下這個時代的句點。

自10奈米的技術世代之後,傳統的微縮技術開始因設計-技術偕同最佳化(design-technology co-optimization,DTCO)而完善,集結來自技術和設計領域的專家。在DTCO的時代,縮減軌道高度和發展更多加速結構微縮技術(structural scaling booster)的作法被採用,標準元件和靜態隨機存取記憶體(static random access memories,SRAM)因而得以微縮至極緊密的程度。舉例來說,加速微縮技術包括自對準閘極觸點(self-aligned gate contact)、金屬閘極截止(metal-gate cut)和超導孔(supervia)。

但隨著我們更進一步發展,並回顧DTCO能在系統單晶片(system-on-chip,SoC)層面帶來的好處,可以想見這些好處會達到某種飽和—尤其是當我們開始注意到系統單晶片的全域存取(global access)和電源供應技術。

因此,以3奈米技術和後續技術節點來說,我們需把微縮技術的重心從邏輯元件層次轉移到系統層次。所以,DTCO正在朝STCO導向的方法進化。

| 圖一 : 從設計—技術偕同最佳化(DTCO)到系統—技術偕同最佳化(STCO) |

|

STCO:去整合的妙方

一般來說,STCO包含系統單晶片的去整合(disintegration)和再整合(reintegration)。系統單晶片由各種(異質的)子系統(功能元件)組成,這些子系統由複雜的佈線圖相互連接。在將系統單晶片去整合的時候,應該巧妙地決定要在內連導線階級中的哪一層分割(partition)系統。

但可以用什麼方法做出這個決定呢?哪些元件歸屬同類?又哪些元件應該分別處理?我們通常必須在導線粒度和技術異質性間取捨,前者指的是系統中的不同零件將以何種粒度重新相連。比方,如果我們想達到非常精密的粒度,就不能重新連接多種不同技術。

去整合之後,這些個別的子系統就能以最合適的技術分別進行設計和處理。

照著去整合和再整合的方法,我們將不再遵照以往一直被用來製作更高階系統單晶片的指導原則:互補式金屬氧化物半導體(complementary metal-oxide-semiconductor,CMOS)的廣用性。

目前為止,晶片上所有的不同功能元件(例如包括:邏輯元件、記憶體、I/O介面、電源元件等)都被連接在同一個CMOS技術平台。對這項CMOS技術進行微縮,目前已發展出性能更高的系統。

但隨著系統單晶片變得越來越異質,採用另一個不同的處理技術會更有利(這項技術也可以是某個技術的多節點變化),以因應子系統的不同需求。比如說,記憶體的處理不需和邏輯元件相容。或者,想想看感應器和其他類比功能元件,運用終極微縮技術其實對這些元件來說沒什麼幫助。就這些功能元件來說,可以採用更簡易的處理過程和間距較寬鬆的微影技術(lithography)。

透過這個方法,我們預期能夠在功率、性能、面積和成本方面獲得更多進展—為將來的電子系統提供微縮的新契機。

再整合:3D整合技術登場解救現況

在去整合系統單晶片和優化不同子系統後,這些子系統需要透過現有的一種3D整合技術,巧妙地再次進行整合。

不同的3D整合技術可應用在內連導線階級中的不同層,囊括具指數級差異的內連導線密度(也就是每平方毫米的連接數)—從毫米級到奈米級。

這項3D內連導線的技術全貌可以下方圖表說明。此圖表描述了有關可實現之3D內連導線密度和間距的各種3D整合方法。

在圖表顯示晶片結構較粗糙的左方,是系統子元件間僅需少數連結時一般會採用的技術。目前零組件的分割是在封裝的階段,透過將封裝(package)相互堆疊完成。動態隨機存取記憶體(dynamic random-access memory,DRAM)的堆疊已展示了這種系統級封裝方法(system-in-a package,SiP),粗接點間距可小至約莫400μm。多晶粒(multiple die)作為一種代替系統級封裝的方法,能在單一封裝中運用被動中介層(passive interposer)來進行整合—又稱2.5D整合。舉例而言,2.5D整合現在正被用來生產「小晶片(chiplet)」型的產品。

或者,扇出型晶圓級封裝產品數量眾多(對諸如智慧型手機的行動應用來說,這是頗受歡迎的解決方案),2.5D整合可以應用在這些產品的其中之一,因為具2.5D整合特色的產品可能得以實現在小配置規格中低成本、寬I/O的晶粒到晶粒互連(die-to-die interconnect)。很多這種技術運用水平和垂直式的內部互連。

3D內連導線的高密度可透過晶粒到晶圓的堆疊技術實現,晶粒成品被黏在經過完全處理的晶圓上。晶粒間以矽穿孔技術(through-Si vias,TSVs)或微凸塊(microbumps)相連。愛美科的目標是將這些微凸塊間的間距縮短至10μm以下。

接下來是實現真正的3D系統單晶片的晶圓接合技術(wafer-to-wafer bonding)。這種系統單晶片是各種功能元件和技術分區進行異質堆疊而成的封裝,其內連導線間距大約是1μm。有兩種技術可供應用:異質晶圓接合技術(hybrid wafer-to-wafer bonding)或介電層晶圓接合技術(dielectric wafer-to-wafer bonding)。

目前最高的內連導線密度是透過循序的處理過程達成。電晶體最終能進行相互堆疊,接觸間距(contact pitch)小至100nm。每當晶片上層需和底層進行微影精度對準時,循序處理的真正用處便浮現。「電路下陣列技術(array under CMOS)」,是一種可能受惠於循序處理的有趣應用—它需將周圍電路和陣列分離。循序處理也可應用在感光元件(imager)和記憶體選擇器(selector for memory)等元件上。

非比尋常的發展藍圖

值得注意的是,我們不該將這張3D技術全貌解讀為由左而右排序的時間表。沒有一個封裝技術能滿足所有需求。

反的,不同3D整合技術相互並存,甚至能在同一系統中共存。

此外,隨著內連導線密度和間距及時改善,每種技術都有各自的發展藍圖。但要決定出哪個是最佳3D整合技術,完全由應用本身和分割後各部件間的「流量」決定。這個最佳技術由多項技術合成,讓單一系統得以整合在更小的配置規格中,且性能、功耗優化,生產成本更低,以支援STCO。

當邏輯元件和3D技術連結:兩件STCO案例

系統單晶片的各種功能元件(像是感光元件或記憶體元件),藉由現有的3D整合技術之一,已應用了分割和再整合技術。然而,截至今日,邏輯元件仍多是被置於「3D設計圖」之外。下述兩件案例說明此議題在近期的改變:邏輯對記憶體異質整合以及晶背電源供電系統的案例。

這兩件案例將說明邏輯元件和3D技術如何在STCO架構中連結,以及設計良好的分隔技術能以什麼方式為未來CMOS微縮技術提供轉機。

這兩件案例中,我們探討系統單晶片的三個關鍵功能元件:邏輯核心、快取記憶體與儲存器、電源供應元件。

邏輯對記憶體的異質整合

在傳統的系統中,記憶體陣列置於其支援的邏輯核心旁。這樣的配置使得內連導線長度居於適中,這個長度由兩元件間的間隙和單一晶粒上的凸塊間隙決定。

或者,系統可以應用功能元件分割和晶圓接合技術,把記憶體垂直堆疊在邏輯元件上方。記憶體可透過記憶體優化的處理程序,在單一晶圓上製造,而邏輯核心可在另一片晶圓上製造。

這麼做的好處包括潛在地縮減晶粒面積,並且明顯地縮減元件的實際尺寸(footprint)。而且還能讓功能元件(如:L2快取)置於距離其支援的邏輯元件更近的位置,平均的內連導線長度便是兩元件間的垂直間隙。這使性能(內連導線頻寬)得到提升,而功率耗損降低。

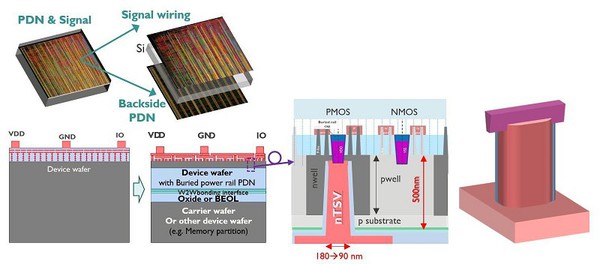

晶背電源供應

電源供應網路(power delivery network)的目標便是提供元件電力和參考電壓給晶粒上的主動元件。這個網路其實就是內連導線的網路,和訊號網路(signal network)截然不同。一直以來,訊號系統和電源供應系統的處理都在半導體的後段製程,也就是位於矽晶圓的前側。

我們也可以想像從晶圓背面提供全域功率(global power)。從晶背那裡,內連導線的網路可和埋入式電軌(buried power rail)連接,這些電軌屬於一種加速微縮技術,以區域電軌的形式在晶片的前端製程中埋入晶片。

| 圖三 : 功能元件的晶背電源供應網路原理是應用奈米級矽穿孔技術,以穿過超薄的矽元件層,接觸埋入式電軌。 |

|

應用上,可以透過先將CMOS晶圓以晶圓接合技術連接在載體上,以進行晶背處理。接著,晶背以極高的薄化程度加工(薄化至大約數百奈米)。如此,從晶圓正面流通至晶背的奈米級矽穿孔得以曝光,並以極精密的粒度相連。

藉由直接從晶背傳輸電力至標準元件,愛美科團隊在近期用實例證明了此技術可帶來減少30%面積的微縮好處。除此之外,在晶背佈建電源供應網路可以讓晶片的正面免於佈建電源網路繞線,能夠降低後段製程的複雜度。還能改善電源電壓下降的問題(或稱壓降,是在後段製程中電阻增加所致),最多能提升15%性能。

有趣的是,這種功能元件晶背處理的概念可以延伸應用至電源供應以外的地方。

我們可能開始想著要在晶背佈建其他功能元件,舉例包含:金屬-絕緣體-金屬電容(metal-insulator-metal capacitor,MIM capacitor)、靜電保護元件(electrostatic discharge devices,ESD devices)或氧化銦鎵鋅電晶體(indium-gallium-zinc-oxid transistor,IGZO transistor)。

結語

隨著DTCO漸漸失去動能,我們正處在新世代的前夕:未來會是STCO的時代,邏輯元件層次的微縮將由全域系統層次的微縮補足。STCO需將系統單晶片去整合,而後應用現有的3D整合技術之一將系統單晶片再整合。這些技術可應用在3D內連導線階級的不同層,從封裝到晶粒、到晶圓、到標準元件,甚至到電晶體。兩件案例:晶粒上邏輯元件的異質整合、晶背電源供應,說明了這個STCO架構正如何影響邏輯元件領域,為接續微縮技術發展之路提供後續關卡的開關。

(本文由愛美科授權刊登;作者Julien Ryckaert為愛美科3D異質整合計畫主持人、Eric Beyne為愛美科3D系統整合計畫主持人;編譯/吳雅婷)

*刊頭圖 (source: wallpapercave.com)