隨著設計規模變得越來越大,功能越來越多,複雜性也在持續呈爆炸式增加。對於整個設計和驗證團隊而言,無論是在時間、工作量和經費上,運作的成本都呈現指數性增長。

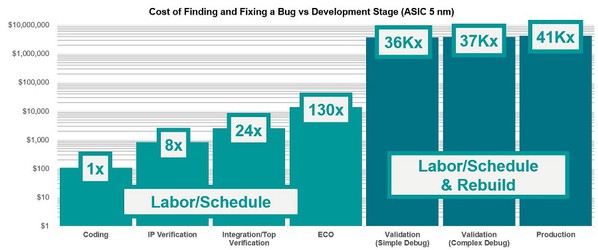

| 圖一 : 若未能儘早發現問題,就需要花更多精力來尋找並修復問題。(source:Wilson Research Group and Siemens EDA, 2020 Functional Verification Study) |

|

造成預算超出和計劃延遲的一個重要原因是設計錯誤,而這些錯誤原本是可以在設計過程中修正的,且不需要用到精密複雜的驗證程式,也不必具備深奧難懂的驗證技術知識。但是,如果這些錯誤轉給驗證和整合團隊時,會導致設計流程停頓下來,迫使驗證工程師將有錯誤的區塊送回至設計工程部門。

解決此問題的最佳方式是,在區塊和子區塊設計期間從源頭修正錯誤。要做到這點,設計師必須改變他們看待並處理驗證和除錯的方式,並且需要工具來幫助他們將合理品質的產品儘快地交給驗證團隊,讓驗證工程師能夠調教區塊並予以整合。

...

...

| 使用者別 |

新聞閱讀限制 |

文章閱讀限制 |

出版品優惠 |

| 一般使用者 |

10則/每30天 |

0則/每30天 |

付費下載 |

| VIP會員 |

無限制 |

25則/每30天 |

付費下載 |