面對開發先進元件時越發嚴峻的微縮瓶頸,半導體開發人員持續積極尋找創新的材料、元件結構與製程來突破物理限制。二維材料是備受全球矚目的新興開發選擇,各界尤其看好這類材料在延續邏輯元件微縮進展方面的潛力。

| 圖一 : 半導體開發人員持續積極尋找創新的材料、元件結構與製程來突破物理限制。 |

|

二維材料,例如二硫化鎢(WS2),在未來邏輯晶片的製造上扮演了關鍵要角。它們具備傑出的材料特性,因此可望實現閘極長度的終極微縮,進而延續邏輯電晶體微縮的發展藍圖。二維材料還可能改變晶片架構的設計思維,帶來革命性的巨變,甚至能讓緊湊型電晶體相容於後段製程,模糊了前段與後段製程之間的分界。

近年來,實驗性二維電晶體的技術成熟度已經大幅提升,而且要將這項技術引進業界的開發途徑也在持續拓展。同時,為了提升元件性能,現有的相關技術挑戰也在著手解決。

必用二維材料的五大理由

[1]二維材料具備多種優異的材料特性

維材料是一種能夠生成二維晶體的材料。這些材料以精練的二維尺寸,展現了優異奪目的電氣學、熱學、化學與光學特性。其中,最著名的就是石墨烯,一種六方晶體蜂窩狀的碳原子層。石墨烯擁有出色的機械強度,具備良好的導熱和導電性能,還有獨特的光學特性。

不過二維材料的開發其實並不僅止於石墨烯。化學式以MX2表示的過度金屬硫族化物(transition metal dichalcogenide;TMD)就具備各式各樣的材料特性,能夠與石墨烯相輔相成。

與石墨烯不同,二硫化鎢、二硫化鉬(MoS2)與一些其他材料具備更廣的能隙範圍,所以是天然的半導體。厚度僅原子等級的二維材料,還能依照其化學組成與結構組態,分成金屬或絕緣體。由於二維材料擁有優秀的材料特性,用於多元領域的契機也已浮現,包含(生物)感測、儲能、光伏電子、光電電子與電晶體微縮。

[2]二維結構的電晶體可望實現閘極長度的終極微縮

在晶片製造上,像是WS2、MoS2的二維半導體逐漸嶄露頭角,成為在電晶體導電通道上取代「往日萬用矽材」的候選材料。而它的關鍵優勢在哪?

基於二維結構的場效電晶體(2D-FET)與矽材相比,預計更不容易受到短通道效應(short-channel effect)影響,而短通道效應已經變成矽基電晶體微縮的主要障礙。確實,隨著矽基電晶體的通道尺寸越做越小,電流開始穿越這些通道,甚至在閘極電壓關閉時仍出現漏電流。這被稱作短通道效應,過去每進入新一代的技術節點,就會變得更嚴重,阻礙閘極長度進一步微縮。

鰭式場效電晶體(FinFET)是目前主流的電晶體技術,能夠在某種程度上遏止這個效應。在這種電晶體結構中,鰭型的通道區域可以變得更薄,而閘極可以不只單面圍繞通道。這能讓閘極電壓更容易控制矽基通道內的載子流動。

即將步入奈米片(nanosheet)設計的新一代電晶體結構則延續了FinFET的設計概念,進一步讓閘極環繞住通道的所有面向,能夠提供更有效的靜電控制。不過當微縮尺寸進入3nm以下,這些矽基結構還是會持續受到短通道效應之害。

這時,具備高遷移率的WS2、MoS2就能派上用場,突破這個設計瓶頸。這些材料只要少數幾層甚至是單層的原子就能構成,因此可能可以生成極薄的通道區域,電流流動的路徑也會因而大幅受限,那麼在元件關閉時,載流子出現滲漏的難度就會更高。如此說來,這些材料可望能實現閘極長度在10nm以下的終極微縮,消除短通道效應帶來的設計疑慮。

愛美科的研究團隊看好這些材料的潛力,近期進行了一項「設計—工程技術偕同最佳化(design-technology co-optimization;DTCO)」的研究,他們展示了2D-FET進一步延續邏輯元件微縮發展的可能性,其中,奈米片電晶體堆疊(stacked nanosheet transistor)的架構是最有可能的切入點。

[3]二維材料可用來建構後段製程的緊湊型開關

除了高性能電晶體,二維半導體的應用還有其他可能。其它深具潛力的應用領域包含低功耗電路,其性能和尺寸的限制都更少,例如片上(on-chip)電源管理系統、訊號緩衝器與記憶體選擇器。此外,二維材料還可能可以用來突破晶片後段製程的限制,打造出能與後段製程相容的小型開關。

晶片製造可以粗略分成兩個部分:製造電晶體的前段製程,以及用多層導線連接電晶體的後段製程,這步驟是要打造出具備特定功能的電路並傳輸電源。傳統電晶體的微縮變得越來越具挑戰性,科學家不斷在尋找新的方法,要在後段製程放入更多的電晶體與小型電路,為前段製程節省一些空間。

不過要做到這點,只能採用可以在相對低溫中進行整合的材料,這樣才不會損傷下層的元件和導線。運用二維材料就有可能實現。

不僅如此,與其他的後段製程做法比較,採用二維結構的電晶體還有另一點好處,那就是它有可能可以建構出n型以及p型元件,這對CMOS邏輯元件來說有其必要。利用二維材料就能在後段製程開發緊湊型CMOS邏輯電路,用來進行電源閘控(power gating)或是作為中繼器(repeater)。

[4]實驗成果顯示超級微縮二維電晶體的高性能

問題來了,我們能實驗性地製造出這種超級微縮的2D-FET嗎?它們有達到預期的性能潛力嗎?近年來,科學家已經探索了多種的MX2材料。最初的結果顯示,基於MoS2的材料發展較為成熟,在實驗中獲得的最高遷移率趨近於200cm2/Vs的理論數值。最近,基於WS2的場效電晶體也有望獲得足以競爭的成果,理論上它具備更高的性能潛力。在改良接觸電阻與增加元件性能方面,也皆已取得進展。

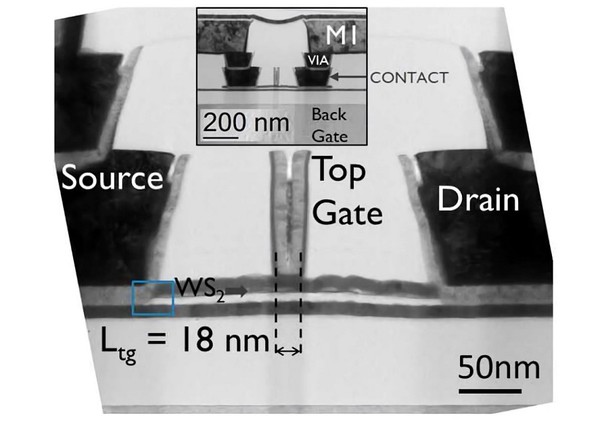

舉例來說,愛美科團隊能夠展示具備完整功能的2D FET,而且一個通道只有1~2層單分子層的厚度,長度為30nm。我們還能用雙閘極的元件結構,獲得更佳的靜電控制能力。傳統FET只有一個閘極,位在頂層,而雙閘極電晶體在頂層和底層各有一個閘極,兩者連接時能增強對通道的靜電控制。

[5]用於業界的2D-FET量產途徑正在開發中

2D-FET要在邏輯技術節點的發展藍圖中獲得一席之地,前提是要能夠量產,這對產業應用來說是關鍵。也就是說,我們要將這些元件帶出實驗室,並整合到12吋晶圓上,生產工具還要符合業界標準。

愛美科已經為此做好準備,並描述了將這些二維材料導入12吋晶圓的整合流程。這套流程是用來研究不同的製程條件帶來的影響,並進一步研究提升元件性能的方法。

在12吋晶圓上生成高品質的二維材料,舉例而言,就能利用金屬有機化學氣相沉積法(MOCVD),該製程以化學反應將晶粒沉積於表面。藉此,沉積的厚度能以單原子層等級的高精準度在完整的12吋晶圓上進行控制。多項實驗結果顯示,950℃的高溫沉積對元件層的結晶度和缺陷有益。

| 圖二 : 利用12吋晶圓製程打造二維元件的穿透式電子顯微鏡(TEM)影像。 |

|

然而,一些更複雜的電晶體架構,例如奈米片堆疊,或是在發展藍圖中屬於更進階的互補式場效電晶體(CFET),可能就需要其他的沉積技術。製造後段製程電路也是一樣,這些電路的熱預算有些限制。所以愛美科也調查了一些替代的沉積技術,還探索了轉移製程的可行性,就是把二維的通道移至已完成部分沉積的12吋矽基板上。

開發二維材料的三大挑戰

不過就現階段,單一元件的性能比已知的那些實驗性元件還低了一個數量級,而12吋晶圓的整合流程就是用來了解製程帶來的影響,以及找出整合的技術障礙。

通道材料的品質以及缺陷控制還是提升元件性能的首要挑戰;另一個挑戰是源極與汲極接觸的接觸電阻,還需要降到可接受範圍;最後,全方位的模型還有待開發,要嵌入在現實投產的假設情境,以實現先前所說的元件架構設計。

(本文由愛美科授權刊登;作者Iuliana Radu為愛美科計畫主持人/編譯:吳雅婷)