無人機、智慧汽車、擴增實境或虛擬實境(AR/VR)頭戴式裝置都使用多個圖像感測器,而且通常是用不同類型的感測器來採集周邊環境相關的資料。為了傳輸系統所需的圖像資料,每個感測器都需要連接到系統的應用處理器(AP),這為嵌入式工程師帶來了諸多設計挑戰。

首先,AP可連接的感測器I/O埠數量有限,所以必須謹慎分配,確保所有需要連接至AP的獨立元件都有埠可用。此外,無人機和AR/VR頭戴式裝置體積相對較小並且使用電池供電,所以這些應用中的元件尺寸必須盡可能小,功耗盡可能低。

解決應用處理器I/O埠不足的方法之一是使用MIPI攝影機序列介面-2(CSI-2)規範中定義的虛擬通道,它能夠將多達16個感測器資料串流整合為單個資料串流,僅佔用一個I/O埠就能將資料發送到AP。實現虛擬通道的首選硬體平台是現場可程式化邏輯閘陣列(FPGA)。其他的硬體平台則需要很長時間來設計,並且可能無法滿足無人機或AR/VR頭戴式裝置等應用所需的低功耗特性。可能有人會說FPGA佔用空間太大、功耗太高,作為虛擬通道的平台不太可行。然而,半導體設計和製造方面的進步已經催生出新一代尺寸更小、功耗更低的FPGA。

行業現狀

消費領域對無人機、智慧汽車和AR/VR頭戴式裝置等產品的需求與日俱增,極大推動了感測器市場的發展。市場研究機構Semico Research認為汽車(年均複合增長率27%)、無人機(年均複合增長率27%)和AR/VR頭戴式裝置(年均複合增長率166%)等應用是推動感測器市場增長的主要動力,並預測截至2022年,半導體OEM廠商每年的圖像感測器出貨量將超過15億片。

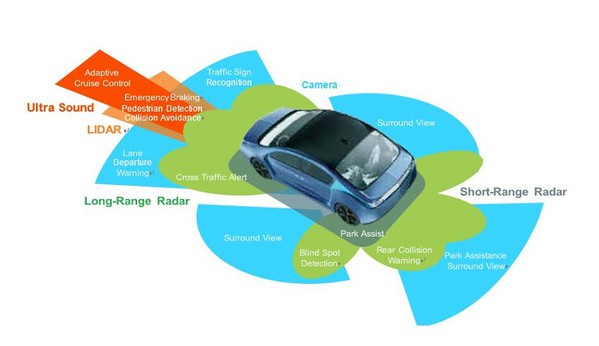

上述應用均需要多個感測器採集環境資料。例如一輛智慧汽車會在後視和環視攝影機系統中使用多個高清圖像感測器,使用雷射雷達感測器用於目標偵測,使用雷達感測器實現盲點監控。

| 圖1 : 如今的智慧汽車需要各類感測器(雷達/光學雷達、圖像、ToF感測器等)實現緊急?車、後視攝影機和碰撞規避等應用。 |

|

感測器數量激增也帶來了難題,因為所有這些感測器都需要向汽車的AP發送資料,而AP的I/O埠數量有限。感測器變多還會增加設備電路板上連接到AP的線路密度,對於頭戴式裝置這樣的小型設備而言,無疑在設計尺寸方面帶來了更多挑戰。

解決應用處理器I/O埠不足的一個方法是使用虛擬通道。它能夠將多個感測器的影像串流整合為單個資料串流,然後僅佔用一個I/O埠就能將資料發送到AP。目前將攝影機感測器連接至AP的常用標準是由MIPI聯盟開發的MIPI攝影機序列介面-2(CSI-2)。CSI-2 可以通過CSI-2虛擬通道功能,將多達16個不同的資料串流整合為單個資料串流。然而將多個不同類型的圖像感測器的資料串流合併為單個影像串流仍然面臨多方面的挑戰。

實現虛擬通道面臨的挑戰

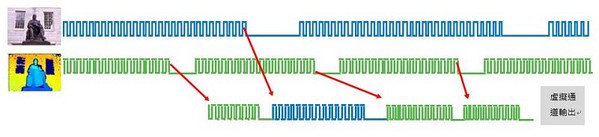

將來自同種感測器的資料合併到一個通道中並不複雜。兩個感測器可以進行同步並將其資料串流連接,作為一張寬度為兩倍的圖像發送到AP。主要的挑戰在於合併不同感測器的資料串流。例如,無人機可以在白天工作時使用高解析度圖像感測器偵測物體,在晚上使用較低解析度的紅外線感測器來採集物體的熱成像以偵測物件。這些感測器的畫面播放速率、解析度和頻寬各不相同,無法同步。為了追蹤不同的影像串流,每個CSI-2資料包需要用虛擬通道識別碼進行標記,方便AP根據需要處理每個資料包。

| 圖2 : 虛擬通道將來自多個不同類型感測器的資料串流合併以節約I/O埠,處理來自不同感測器的資料串流,需要同步時脈速率和輸出頻率。 |

|

除了標記資料包之外,合併來自不同類型感測器的資料串流,還需要同步感測器資料有效負載。如果感測器以不同的時脈速率運行,則每個感測器需要保持單獨的時鐘域。然後在傳輸到AP之前將這些時鐘域進行同步。

虛擬通道需要專門的硬體橋接處理

通過硬體實現支援虛擬通道的橋接解決方案可以解決上述問題。使用專用的虛擬通道橋接意味著所有圖像感測器都連接到橋接I/O埠,然後再通過單個埠連接到AP,釋放寶貴的AP埠以支援其他週邊元件。這也解決了設備電路板上感測器與AP之間存在過多連接而產生的設計尺寸難題;橋接方案將這些線路合併連接到AP。

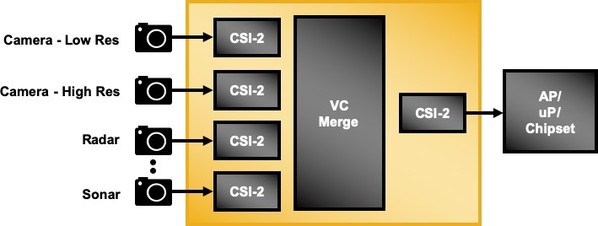

| 圖3 : 為了最大限度地減少連接感測器和AP的I/O埠,支援虛擬通道的硬體橋接方案整合了多個感測器資料串流,通過單個I/O埠進行傳輸。 |

|

FPGA可以為每個感測器輸入實現並行的資料通道,每個通道都有自己的時鐘域。如圖3所示,這些時鐘域在虛擬通道的合併階段同步,從而減輕了AP的處理負擔。

基於PLD的虛擬通道硬體的優點

在硬體上實現虛擬通道,FPGA是最可靠的IC平台。FPGA具有靈活的I/O埠,可支援各種介面,並且擁有可以使用硬體描述語言(如Verilog)程式設計的大型邏輯陣列。與需要冗長設計和QA流程的ASIC不同,FPGA在生產時已通過QA驗證,可以在幾天或幾周內完成設計。然而人們通常認為傳統的FPGA體積龐大,耗電量高,並不適合功耗有限的嵌入式應用。但FPGA已今非昔比。

萊迪思半導體的CrossLink系列FPGA為使用虛擬通道的影像橋接應用提供了性能、尺寸和功耗的組合。該系列可提供兩個4通道MIPI D-PHY收發器,每個PHY速率高達6 Gbps,尺寸最小僅為6 mm2。它們支援多達15個可程式化設計源同步差分I/O對,如MIPI-D-PHY、LVDS、sub-LVDS,甚至單端並行CMOS;在許多應用中功耗不到100 mW。CrossLink FPGA系列支援睡眠模式,減少待機時的功耗。萊迪思還提供全面的軟體IP函式庫,協助客戶更快地實現不同類型的橋接解決方案。

總結

MIPI攝影機序列介面-2(CSI-2)規範的虛擬通道可協助嵌入式工程師在單個I/O埠上整合多個感測器資料串流,從而減少使用大量圖像感測器應用的總體設計尺寸和功耗。憑藉著可重新程式設計特性以及性能和尺寸上的優勢,萊迪思半導體的CrossLink系列低功耗FPGA可以讓客戶快速、輕鬆地為其設計新增對虛擬通道的支援。