因應近年來人工智慧(AI)熱潮推波助瀾下,包括NVIDIA、AMD、Amazon等科技巨頭無不廣設資料中心,備妥「算力軍火庫」。因此帶動龐大AI先進製程晶片需求,卻也造就台灣半導體代工產業鏈產能缺口,分別投入矽光子等先進封裝製程布新局。

目前所稱「先進封裝」技術中的亮點,「扇出型封裝」(Fan-Out Packaging)又可再細分為:扇出型「晶圓級」封裝(Fan-Out Wafer-Level Packaging;FOWLP)已投入應用多年,進而投入發展扇出型「面板級」封裝(Fan-Out Panel-Level Packaging;FOPLP)。預估在高效能運算(HPC)、AI應用驅動下,2024年面板級封裝市場規模約為11億美元、2029年達到69.4億美元,2024~2029年複合成長率約44.56%。

兩者最大差異則在於尺寸和利用率。由於FOPLP將IC封裝基板從圓形改為方形,可使封裝尺寸更大,擁有更高的生產靈活性;基板材料也可以改用金屬、玻璃或其它高分子聚合物材料取代矽,又以玻璃基板在機械、物理、光學等性能上更具優越性。

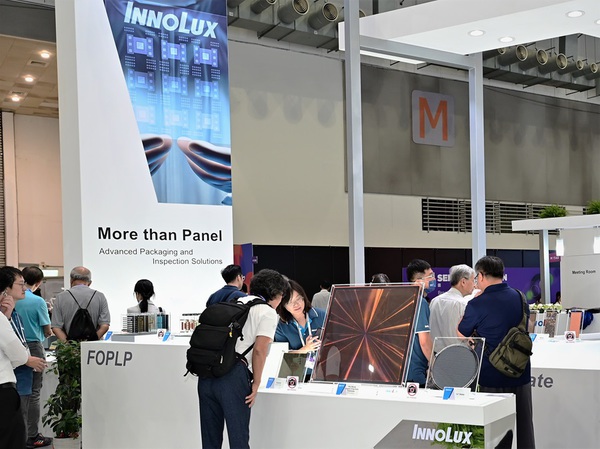

面板級封裝化圓為方 以空間擴產能

在相同晶圓單位面積的使用率上,方形基板以FOPLP >95%面積使用率,力壓傳統FOWLP晶圓封裝<85%的面積使用率,具備可大批生產、成本低與生產周期短等優勢,以提高生產效率、產量,相對減少切割過程中浪費的材料和成本,還盼可藉此緩解CoWoS吃緊產能。

| 圖一 : 由於FOPLP將IC封裝基板從圓形改為方形,吸引PCB載板和FPD面板製造廠商積極投入。(攝影:陳念舜) |

|

一旦改為玻璃基板後,業界既不必擔心載板會隨著IC越來越大而翹曲;還可容納封裝更多的裸晶單位及I/O數,達到高密度連接和輕薄的封裝,提升封裝後元件效能;以及體積更小、效能更強大,又節省電力消耗等技術優勢。降低蝕刻和電鍍製程成本,而減少材料消耗;加上無須打線、凸塊,可望降低每單位封裝成本達30%;並在單一晶片上整合更多功能,從而以更低的成本實現輕薄產品,改善電氣和散熱性能。

舉目前市場主流的510mmx510mm方型基板為例,可使用面積是既有12吋晶圓的3倍,不但可以塞下更多的晶片,也可大幅提升產能與降低每單位封裝成本。估計現今扇出封裝約占整個先進封裝市場約10%,面板級解決方案又僅佔整個扇出市場10%。更吸引晶圓廠與傳統OSAT封測、整合元件大廠(IDM),以及PCB載板和FPD面板製造廠商積極投入。

現已涉入FOPLP封裝業務的廠商發展的玻璃基板尺寸,大致可區分為:515x510mm主要採用者包括力成、矽品等;日月光除了採用300x300mm尺寸外,也採用了600x600mm的玻璃基板規格。已有供應鏈業者透露,台積電本來選擇的玻璃基板尺寸是515x510mm,但最近新定案的版本則是與日月光相同的600x600mm。

導入TGV先進加工技術 發揮通電性能潛力

且隨著AI晶片,高頻高速通訊設備和元件需求的快速增長,日益凸顯玻璃基板在先進封裝技術中的重要性。比起有機銅箔基板電阻值低,減少晶片發熱特性,具有更密集的布線能力與更高的訊號性能潛力,因此效率較佳,可靠度也表現更好。且因玻璃的平坦度極高,可承受高溫和高電壓,最適合車用IC、高壓IC等晶片,無論是電池、高功率快充等都能派上用場,被視為傳統基板的理想替代方案。

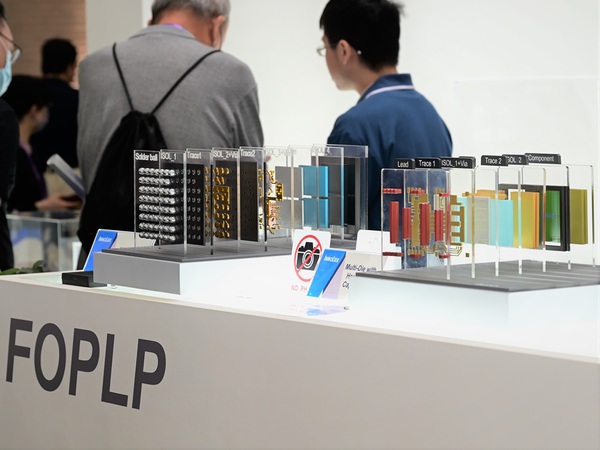

| 圖二 : 隨著AI晶片,高頻高速通訊設備和元件需求的快速增長,日益凸顯玻璃基板在先進封裝技術中的重要性。(攝影:陳念舜) |

|

如今主流玻璃基板的尺寸為515x510mm,在半導體和載板製程中均屬於全新製程,涵蓋玻璃金屬化(Glass Metallization)、後續的ABF壓合製程,及最終的玻璃基板切割。在玻璃金屬化完成後的玻璃又稱做「Glass Core」,製程涉及TGV(Through-Glass Via)、濕蝕刻(Wet Etching)、AOI光學檢測、鍍膜(Sputtering)及電鍍(Plating)。

過去FOPLP遲遲未能普及應用的關鍵,便在於良率與品質的問題一直無法克服,像是玻璃容易破碎或是加工難度較高等;更重要的是,相關的封裝材料、製程設備都需要重新開發與設計。

其關鍵的第一道工序「TGV」技術儘管早在10年前就已問世,但其速度未能滿足量產需求,僅能達到每秒10~50個孔,使得玻璃基板技術至今尚未能起飛。台灣的鈦昇科技自從5年前與北美IDM客戶合作研發TGV技術,並於去年成功通過製程驗證之後,已能實現每秒8000個孔(固定圖形、矩陣型)或每秒600~1000個孔(客製化圖形、隨機分布類型),且精準度可達±5μm,符合3 sigma標準內,使玻璃基板終於達到量產規模。

並在今年SEMICON Taiwan展現聯合發展玻璃基板中的核心技術Glass Core製程,共同完成515x510mm尺寸玻璃glass core樣品,涵蓋了從雷射改質、蝕刻通孔、種子層鍍膜等製程。且提供針對ABF後玻璃雷射切割的雷射倒角(Laser Beveling)與雷射拋光(Laser Polishing)解決方案。

| 圖三 : 鈦昇科技在今年SEMICON Taiwan展現玻璃基板雷射加工的完整解決方案。(攝影:陳念舜) |

|

掌握玻璃特性和成本優勢 面板廠投入FOPLP後發先至

且有群創等以玻璃基板為主的面板廠業者,與工研院、強茂等業者共同投入研發FOPLP的時間也已經長達8年,無論是材料、設備等供應鏈勢必加快速度跟上持續擴產因應,將成為未來高階封裝技術的趨勢之一。

既可活化群創3.5代舊面板廠產線,6~7成設備與工程師皆可沿用,已折舊完畢的廠房及設備成本競爭力亦為競逐訂單的重要利基,又因為擁有生產製造的Know How,對於大尺寸玻璃面板搬運及加工特性早就瞭如指掌,造就跨入FOPLP最大優勢,分別發展700 x 700 mm(RDL first製程)、620 x 750 mm(Chip first製程)尺寸面板。

未來,群創將成為匯聚半導體與面板於一身的廠家,同時也是業界首創的全球第一條面板產線轉型封裝應用的案例。但主要是其目前以生產成熟製程的PMIC為主,後續還需要進一步發展,才有機會朝AI GPU等級的FOPLP方向前進。

工研院指引FOPLP關鍵 已建立完整研發能量

工研院機械所組長黃萌祺也在今年SEMICON Taiwan舉行的「半導體先進封裝技術論壇」上,分析現今FOPLP所使用的技術與設備,將因為玻璃基板具有比晶圓更高剛性,減緩傳統異質整合的翹曲問題;與晶圓差不多的低膨脹係數和介電損失(Df)的特性,可滿足先進封裝低熱變形及高頻/高速傳輸應用情境需求,將互連密度提高10倍以上,可直接與高頻晶片、天線共同封裝,成為異質整合技術的重要關鍵模組。

此外,玻璃基板因為夠平整,可用來製作高密度RDL,滿足翹曲度與載板細微線路(<3μm)問題。針對目前CoWos封裝包含晶片、中介層、載板,玻璃可用來取代傳統矽質中介層,所以會要求達到200~300μm<500μm的極薄程度;若要能取代下方IC載板,還須選擇500μm以上厚度,達到800μm或1mm、孔徑和玻璃厚度的深/寬比約1:10,以達到一定密度也避免易碎風險,未來還會朝更高深/寬比發展。

工研院目前也以半導體技術為核心,結合模擬設計、智慧化監控等技術,開發具競爭力與節能減碳的關鍵設備,帶動半導體和PCB產業發展,提升台灣半導體與電子設備暨關鍵零組件自主化。黃萌祺也在工研院機械所帶領旗下電漿、溼式、研拋、低氟/低碳4大設備團隊。

由於玻璃具有易脆性,所以玻璃封裝基板需要高深寬比(AR>10)通孔製程,以滿足線路密度與製程可操作性需求,TGV基板厚度應限制在≧300~800μmm。須開發項目則包含:

1.鑽孔:雷射改質+蝕刻製程設備,藉此避免玻璃微裂,有別於傳統面少了線路,毋須鑽孔、填銅;

2.附著層:PVD或濕式製程設備擴大以配合高深寬比需求,因此增加成本與技術限制,所以開始有廠商思考以濕製程表面處理來取代PVD;

3.填銅:高深寬比填銅設備,可在玻璃鑽孔後填銅來確保不會有缺陷,包覆銅鍍液在內,則應避免造成後續可靠度驗證時元件燒燬;

4.研拋:面銅平坦化設備;

5.檢測:光學、X-ray等檢測設備,前者主要針對玻璃鑽孔、後者針對填銅設備,如今更發展出了複合式檢測設備,,並由工研院提供模組和演算法;

6.接合:ABF與超薄玻璃的壓合設備。

目前還待克服的重點之一,則是玻璃須先經過特殊波長的雷射照過改質後的蝕刻效率及表面品質雖然較佳,卻有耗時3~4hrs太長的缺點,越高深寬比的蝕刻時間與難度更高,工研院現也正與德國等大廠討論,如何在TGV階段能以超快雷射一發鑽孔貫通玻璃的可行性。

至於現今玻璃基板的尺寸主流為510mmx515mm,也有面板廠希望能做到600mmx700mm以加速成本下降,但黃萌祺認為:「未來還須考量先進封裝成熟度,以良率優先,也不排除玻璃和有機載板共存發展的可能性。」

矽光子通透AI任意門 以時間換空間散熱增效

針對目前生成式AI興起之後,對伺服器的效能及資料傳輸環節帶來極大考驗,光訊號的頻寬比電訊號高出許多,無論是在資料中心或雲端主機板高速運算的晶片與晶片、伺服器與伺服器之間的短、中距通訊,將會變成主要的通訊型態。

包含即將進入量產的大型平行光學元件(Large Parallel Optics;LPO),與共同封裝光學元件(Co-Packaged Optics;CPO),都是以2.5D先進封裝的方式來整合EIC及PIC,以縮小元件尺寸,並達到低延遲、低功耗和其他的優點。但最大缺點就是成本高,無法更換單一元件。

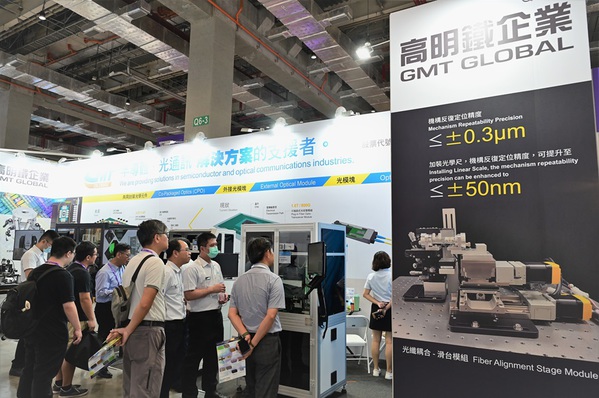

因此在產業發展過程中,除了引進半導體先進封裝和測試設備商,也吸引從事光學鏡頭、太陽能產業的光電測試設備商、滑台系統和對位模組廠商升級和轉型。在光通訊及半導體產業對於CPO需求增加之下,高明鐵近年來便展現轉型成效,推出高精密度耦合對位系統,銷售利基在於高精度的機械設計及根據核心技術開發搭配的應用軟體,主要競爭對手為日本及德國廠商,正與全球國際AI伺服器領導廠商,以及台灣光纖被動元件與模組製造大廠洽談合作。

| 圖四 : 在光通訊及半導體產業對於CPO需求增加之下,高明鐵近期推出高精密度耦合對位系統,與德日廠商競爭。(攝影:陳念舜) |

|

工研院也在2018年成立「矽光子積體光電系統量測實驗室」,提供8吋與12吋晶圓級光電元件自動化快速檢測,包括元件設計、製程整合、光學封裝及光電測試技術,串聯國家矽光子上下游產業鏈。

工研院光電所組長方彥翔中指出,由於5G、AI及雲端服務的快速發展,算力至今已成長千倍以上,造成大量耗電,引發熱管理與功耗挑戰,勢必要大幅加快傳訊速度。矽光子技術因此應運而生,除了利用CPO將先進光學元件(又稱光引擎)與ASIC等矽基元件,整合在單一封裝基板上;並整合光纖、數位訊號處理(DSP)、交換器ASIC等先進封測技術,利用光訊號在長距離傳輸中的低損耗特性,大幅提升系統的傳輸效率。

從2015年可插拔光學(Pluggable Optics)光收發模組的100G數據傳輸速率,包含放大器、光纖等元件將被CPO矽封裝製程組合的光元件逐步取代,實現將光通訊模組和光交換晶片整合在同一封裝基板,PIC光子積體電路與EIC電子積體電路也成為CPO技術備受討論的關鍵議題。

藉此可提供更短的光學路徑,從而達到最佳傳輸性能和最低功耗;同時降低系統複雜度,解決晶片及封裝層面的互連挑戰。至於每個AI伺服器櫃內的板子間,還會存在許多GPU、HBM等都通過銅線傳訊為主,甚至會改以LED光傳輸,也不像雷射一樣容易受到溫度影響,實現在極短距離內高速傳輸目標。工研院也自2018年起在政府支持下,開始著手建立完整試製平台,並領先全台引進首部可測得200G下的晶片頻寬、供電訊號速度的測試設備。